當前位置: 首頁 > 工業電子產品 > 其他電子產品 > 開發板,套件,編程器 > 開發板

發布日期:2022-10-14 點擊率:113

串擾(Crosstalk)是指信號線之間由于互容(信號線之間的空氣介質相當于容性負載),互感(高頻信號的電磁場相互耦合)而產生的干擾,由于這種耦合的存在,當一些信號電平發生變化的時候,在附近的信號線上就會感應出電壓(噪聲),在電路設計中,抑制串擾最簡單的方法就是在PCB Layout中遵循3W原則。

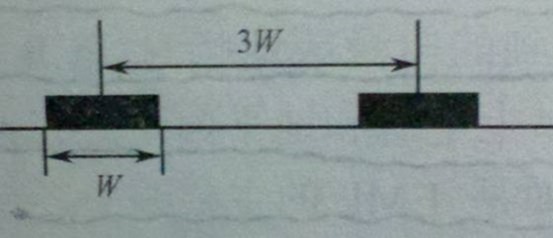

3W原則是指多個高速信號線長距離走線的時候,其間距應該遵循3W原則,如下圖1所示,3W原則要求相鄰信號線中心距離不能少于線寬的3倍,據一些資料記載的,滿足3W原則能使信號間的串擾減少70%。我們在對高速信號,例如DDR3,PCIE,SATA2等布線的時候都會遵循這個原則。

圖1

圖2

本文來自合作伙伴投稿,作者Robin, Jiang,郵箱804037583@qq.com。

下一篇: PLC、DCS、FCS三大控

上一篇: DCDC芯片輸出電壓出現